继光刻机之后,EDA 有望成为集成电路产业新的出圈词汇。

随着 BIS 的出口管制得到全球前三大 EDA 供应商陆续证实,中国集成电路产业链再度迎来考验。

EDA 全称 Electronic Design Automation(电子设计自动化),是芯片生产使用的工业软件的总称,类似于建筑设计的 CAD 软件——事实上,EDA 最初就被视为 CAD 的一个分支。

作为芯片工程师的 Photoshop,EDA 把画电路变成了素材排列组合+写代码,几乎贯穿芯片生产的整个生命周期。ASML 用来校准光刻机镜头的专业软件,便出自 EDA 开发商新思科技之手。

一旦离开了 EDA 工具,想在指甲盖大小的芯片里集成上百亿晶体管,无疑是天方夜谭。

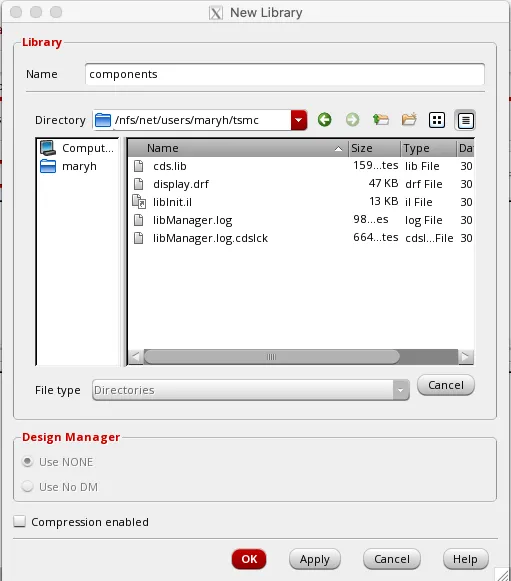

用于芯片设计的 EDA 软件

相比半导体设备市场欧、美、日多家龙头相互制约、相对分散的竞争格局,前三大 EDA 厂商垄断了近 80% 的市场份额,且均为美国公司。与之对应,国内 EDA 爬坡多年,国产替代率仅勉强超过 10%[2]。

EDA 是美国集成电路产业优势最大的板块,也是国内产业链最薄弱的环节。

自动化与分工

EDA 与集成电路产业几乎同步出现,其诞生初衷是把设计电路从画图的体力活变成写代码的脑力活。

1966 年,大名鼎鼎的仙童半导体从 IBM 挖来了工程师 James Koford,直接汇报给公司创始人,也是 「摩尔定律」 的提出者戈登·摩尔本人,具体任务是设计一套方案,代替人力完成芯片的版图绘制、测试、布线等必要步骤。

当时,芯片设计师在完成逻辑电路设计后,需要在图纸上手绘出晶体管及连接导线,即版图。后续制造环节用到的各类器件、材料 (包括光刻用的掩膜版),都基于这份版图完成的,对准确性要求极高,一旦出错就要全盘推倒重来。

仙童半导体制造的芯片 (按照晶体管密集程度排列)

当一块电路板上只有十几个晶体管时,手绘版图难度自然不大,但当晶体管数量扩大到 100 个以上,容错率就相当低了。

一颗包含 150 个电路模块 (一个模块里集成了许多晶体管)的芯片,要耗费四个工程师一周的时间,俨然劳动密集型产业。

1955 年的索尼 TR-55 收音机里集成了 5 个晶体管;70 年后,英伟达在 B200 芯片里塞进了足足 2080 亿个晶体管。如果没有 EDA 工具,工作量难以想象。

有 IBM 的开发经验打底,James Koford 和团队顺利完成任务,开发出了逻辑模拟器、测试程序生成器以及自动布局布线软件[4],成功将四个工程师/一周的工时缩减到了一个工程师/一天。

现代的自动布局布线软件

以此为开端,EDA开始成为加快芯片生产流程的必备工具。

到 70 年代,摩托罗拉等芯片公司都开始用上了内部开发的 EDA 工具。但一方面,当时的 EDA 工具大多种类有限、功能简陋;另一方面,每家半导体公司的 EDA 工具都只 「适配」 自家的芯片设计,在整个产业的战略价值也相对有限。

1974 年,英特尔在以色列法海建立研发中心,核心工作就是研发更好的 EDA 工具,以支持 80286 等一系列 CPU 的设计,负责人就是去年底黯然下台的英特尔 CEO 帕特·基辛格 (PatGelsinger)。

80386 开发团队,基辛格为右二

当时,英特尔总部需要定期将芯片设计的软件版本从加州发送到以色列海法,后者编写程序、完成自动化后,送回加州再进行生产制造。70 年代还没有飞书和 Slack,效率可想而知。

而伴随芯片生产环节不断细分,EDA 软件也愈发繁杂,为了保证开发效率,英特尔只能把 EDA 研发部门分成三个环节,每个环节细分成四个部门,分散在全球十几个研究中心。

持续的研发投入和沉重的管理负担,推动了 EDA 软件最大的一次变革:EDA 从半导体公司的研发部门变成了一个独立的产业,第三方 EDA 供应商开始出现。

1985 年,通用电气率先将其 EDA 部门拆分成为一家独立公司,并改名为新思科技。这一时期创立的还有 Mentor Graphics 和 Cadence,如今的 EDA 三大巨头正式集结。

由于芯片设计和生产需要的投资越来越大,英特尔、AMD 这类芯片公司也乐于使用第三方工具,为自己节约成本。三巨头凭借与顶级芯片公司的绑定关系,逐步确立了领导地位,一直延续至今。

同一时期,中国的 EDA 软件也开始蹒跚起步。

蜜糖与砒霜

1988 年秋天,北京集成电路设计中心汇聚了来自全国 17 家单位的 120 多名学者和技术人员,国内第一套自研 EDA 软件——「ICCADⅢ级系统」 开发工作就此铺开 [6]。

中国第一家集成电路专业化工厂成立在 1978 年,虽然 3 英寸设备可以从日本和美国引进 [7],但 EDA 却受限于 「巴统协议」,无法使用海外先进产品,与全球水平隔了几个世代,严重制约了国内芯片研发的发展。

「巴统」 全称巴黎统筹委员会,由美英国等 17 个西方国家在 1949 年组建,对冷战的另一方实施战略物资和高技术产品的封锁,EDA 作为芯片生产的关键工具,自然是重点把控对象。

「ICCADⅢ级系统」 上马的背景,便是这种技术封锁之下的自主化。

五年后的 1993 年,包含 28 个设计工具的 EDA 软件 「熊猫系统」 问世,虽然称不上世界一流,但对缺少先进 EDA 软件的国内芯片设计公司来说,已然雪中送炭,短时间内就被 20 多家设计公司和研究机构采用。

EDA作为典型的干中学、学中干工种,需要在具体的芯片设计环节中不断积累经验改进产品。当时,「熊猫系统」 定价便宜大碗,甚至还有美国芯片公司禁不住诱惑前来询价 [6],看上去进展一切顺利。

然而 「熊猫系统」 问世第二年,「巴统」 伴随苏联解体失去了存在价值,封锁和管制彻底放开,三巨头之一的 Cadence 当年就宣布进入中国市场,次年,新思科技和 Mentors Graphics 也拍马赶到。

EDA 工具成长的关键是不怕不好用,只怕没人用,海外三巨头自然很清楚这一点。面对初生的假想敌 「熊猫系统」,Cadence 对双方重合的工具大幅降价甚至免费提供,再利用自身更齐全的工具箱和经过验证的成熟方案,迅速抢占市场。

面对这种降维打击,「熊猫系统」 自然难以招架,遗憾折戟。

「熊猫系统」 偃旗息鼓后,三巨头又将战略方向转向了高校和科研机构。1995 年,新思科技一口气向清华大学捐赠了 20 套价值百万美元的 Design Compiler,同时成立对应的电子设计中心,慷慨的不像资本主义世界的公司。

每家 EDA 开发商都有自己的数据格式和使用逻辑,彼此并不兼容。类似于不同语种的学习,新思科技的目的,是试图让自己的 EDA 工具成为芯片工程师的 「母语」,虽然客观上推动了国内芯片设计的进步,但让集成电路产业对自己产生了依赖。

一本武林秘籍练久了就会形成心得和肌肉记忆,用惯了新思编程软件的工程师,不一定能适应 Cadence 的编程环境。同时期国产操作系统和 Windows 有来有回,当时有媒体请还是金山总经理的雷军点评微软,后者说了句意味深长的话:

「世界上没有白吃的代价,人家撒网,让你来钻。」

中国的 EDA 软件就像一本残缺的武林秘籍,纵使招式齐全,但没有受众,终究无法开门立派,就此与国内芯片设计的发展节奏脱钩,划上了一个充满遗憾的句号。

被掐住的七寸

BIS 上一次针对中国发布 EDA 出口禁令是在 2022 年,此次全面断供,除了打击范围更广之外,也给国内集成电路产业的未来蒙上了一层迷雾。

EDA 公司大多采用固定期间授权的方式,假设芯片设计公司签了 3 年的授权合同,在这 3 年内,设计公司不仅能用完整的 EDA 工具,还能获得软件更新和对应的技术支持。

根据新思科技的解释,中国公司此前取得的授权仍然有效,但倘若 BIS 禁令落实,合同有效期过后将无法续签,意味着中国公司无法获得后续的更新和支持。

如果无法使用最先进的 EDA 工具,对中国公司最直接的影响是难以跟上先进工艺的进步节奏,比如先进制程芯片的流片和生产。

流片可以理解为代工厂为生产芯片前的 「试产」,用来测试芯片的功能性能是否符合设计预期,并验证芯片设计方案与代工厂的工艺适配,这其中涉及一个关键的概念——PDK。

PDK 全称 Process Design Kit,即工艺设计包,可以理解为代工厂某一节点的用户使用说明」,其中包括这一节点的设计规则、仿真模型、技术文件等设计参数 [8]。

台积电的 PDK

假设一家芯片公司的一款芯片需要在台积电 3nm 制程上制造,就需要台积电提供 3nm 的 PDK,芯片公司根据 PDK 的参数指导进行芯片设计,否则将导致芯片与台积电 3nm 工艺适配度不过关,达不到流片标准。

这与 EDA 软件有什么关系呢?别忘了,EDA 软件的客户除了设计公司,还有芯片代工厂。

台积电的 N2 节点就点满了 Cadence 和新思科技的工具链,制作 PDK 也采用了后者的 EDA 工具。芯片设计公司如果没有事前取得 EDA 厂商的授权,连 PDK 都打不开,更别说流片了。

台积电 2nm 采用的不同厂商的 EDA 工具

而对于 3nm 等先进工艺节点,代工厂还会时不时改良翻新,比如台积电 3nm 至今为止已经推出了 N3B、N3E、N3P、N3X 四个版本,每个版本都对应不同的 PDK,需要 EDA 厂商同步更新相关工具。

一旦 EDA 厂商停止向芯片设计公司授权,意味着后者无法取得代工厂最新的 PDK,基于新工艺的设计和流片同样无从谈起。

PDK是EDA公司、芯片设计公司、代工厂以及整个集成电路产业链共生关系的缩影。

集成电路产业经过漫长时间的分工与整合,产业链上下游的各个环节,存在着 「互相适配」 的绑定关系。

一颗芯片从设计到封装完成,需要用到 ARM 的指令集和架构、Cadence 的 EDA 工具、Toppan 的掩模版、ASML 的光刻机、东京电子的刻蚀机、KLA 的封测设备、信越化学的硅晶圆、霍尼韦尔的靶材、东京应化的光刻胶等等。

在摩尔定律的推进过程中,每个环节的研发和改进都需要上下游环节的配合协作、相互适配,由此形成了环环相扣的共同体。这个过程中积累的 Know How 会成为某种意义上的 「标准」,进一步拉高行业门槛。

集成电路产业的发展,可以看作产业链每个环节肩并肩在摩尔定律的跑道上奔跑。其残酷之处在于,没有人会停下来等掉队的人。一旦跟不上大部队的节奏,追赶的代价就会成倍增加。

美国 EDA 三巨头在 90 年代的高速增长的原因,是他们与同时期最顶级的半导体公司一起经历了集成电路产业进步最快的阶段,通过一系列收购参与了 「标准」 的确立。

另一方面,伴随集成电路产业分工的细化,每一个环节的技术难度和投资规模都望而生畏,进一步提高了挑战者面临的困难。

上世纪 70 年代,日本通产省牵头,集合富士通、日立、三菱、东芝、NEC 五家公司,「仅仅」 用了 290 亿日元的财政补贴,就换来了 4000 多件技术专利和一条完整的半导体产业链:做材料的京瓷和住友,做掩模版的 TOPPAN,做设备的东京电子,和做光刻机的佳能和尼康。

时至今日,仅台积电一家公司一年的资本开支就逼近 400 亿美元,想要复刻日本人当年的成绩,几乎是天方夜谭。

中国大陆集成电路产业的薄弱,一个重要原因是在产业高速迭代的周期参与度不足,导致错过了产业标准和规则的适配过程。

这也一定程度揭示了国内 EDA 工具发展困境的真相:并非程序员不够努力,而是整个产业链在全球分工中的存在感不足。

尾声

2023 年,华为轮值董事长徐直军曾宣布实现 14nm EDA 工具全链条国产化 [9],不可忽视的大背景,是 14nm 工艺从设计、制造、到封测的国产供应链的全线打通。

同样,要实现更先进工艺的国产 EDA 工具突破,也需要上下游一起进步。

无论是芯片设计、芯片制造还是 EDA 工具,它们终究是一个 「工程问题」 而非 「科学问题」。两者的核心区别在于,科学问题是一道答案未知的数学题,有可能题目本身就是错的;但工程问题有明确的解,能不能做出来考验自身能力。

EDA 工具的特殊性在于,它在商业上类似操作系统和指令集,竞争力很大程度上来自产业上下游共同构建的生态。换句话说,不怕你反复摇摆,就怕你下决心另起炉灶。

当年 「熊猫系统」 的诞生,恰恰来自密不透风的封锁,过去数十年里,中国集成电路产业面对的绝望,也远不止这一次。

参考资料

[1]Synopsys at Bank of America Conference:Navigating Regulatory Challenges

[2] 中国 EDA 产业白皮书

[3]1966:Computer Aided Design Tools Developed for ICs,Computer History Museum

[4]Oral History of Fairchild Micromosaic and Micromatrix Programs,Computer History Museum

[5]Coping with the Complexity of Microprocessor Design at Intel–A CAD History,Pat Gelsinger

[6] 错失 15 年的中国 EDA 产业,最终走上崛起之路,集微网

[7] 未曾忘却的记忆:回旋在酒仙桥地区的集成电路梦,朱贻玮

[8] 什么是 PDK?它在半导体产业起着什么样的作用,OFweek 电子工程网

[9] 突破 「乌江天险」,实现战略突围——徐直军在硬、软件工具誓师大会上的讲话,徐直军