文 | 半导体产业纵横

RISC-V 作为后起之秀,近年来备受追捧。

前不久国内 RISC-V 第一股冲刺 IPO 的消息,更将行业对其商业化的关注度推向新高。

RISC-V 第一股,冲击 IPO

5 月 30 日,国内 RISC-V 芯片龙头企业,北京奕斯伟计算技术股份有限公司正式向港交所递交招股书,开启港股上市征程。

该公司成立于 2019 年,采用新一代 RISC-V 计算架构,创新领域专用算法和 IP 模块,构建高效开放的软硬件平台,为全球客户提供系统级解决方案。

根据弗若斯特沙利文的资料,奕斯伟计算是 2024 年为止中国 RISC-V 主控量产解决方案数量最多的提供商;按 2024 年相关收入计算,奕斯伟计算是中国最大的 RISC-V 全定制解决方案提供商。

由于 X86 和 ARM 架构的长期垄断,RISC-V 架构成为了很多芯片厂商未来的发展方向。中国工程院院士倪光南就曾指出,目前 CPU 市场主要被 x86 和 Arm 架构所垄断,而中国想要打破这个局面,实现自主可控,开源的 RISC-V 架构将是一大机遇和发展方向。

在今年 2 月底的 2025 中国 RISC-V 生态大会上,奕斯伟集团董事长王东升带来重磅 RISC-V 高性能创新成果,奕斯伟计算 64 位 RISC-V 双 Die AI SoC 芯片——EIC7702X,引发广泛关注。该芯片集成 8 核 64 位 RISC-V 乱序执行 CPU、自研 NPU 以及双 GPU 多计算单元,算力可达 40 TOPS(INT8);在图像/语音识别、文本生成等场景展现超低延迟优势。

在业内对 RISC-V 的多次讨论中,应用已成为另一个关注焦点。

国产 RISC-V MCU,十分能打

在 RISC-V 的应用场景中,MCU 是重要的应用领域之一。

在 MCU 市场,Arm 内核目前占比最大,其生态比较健全,架构也已经完善成熟了,因此应用十分广泛。但 Arm 内核局限于封闭的指令集架构、授权及专利费用,不方便细分定制。此外,不同 Arm 内核的性能差异较大,而随着 Arm 内核工作频率的提升,MCU 芯片的能耗增加很快。因此,采用高主频 Arm 内核的 MCU 芯片如何降低能耗,这对 MCU 厂商来说是个不小的挑战。

在处理器内核的选择上,除 Arm 外,RISC-V 架构正在崭露头角。RISC-V 是完全开源的指令集架构,无需支付授权费用,这对成本敏感的 MCU 市场至关重要。此外,RISC-V 的模块化设计允许厂商根据具体需求灵活裁剪指令集。基础指令集 (如 RV32I) 仅 40 余条,而扩展指令集 (如 M、F、D、C 等) 可按需添加,形成定制化架构。RISC-V 的精简架构天然适合低功耗设计。

RISC-V MCU,有几款热门产品。分别为沁恒微的 CH32V307;乐鑫科技的 ESP32 系列、先楫的 HPM6750 系列、兆易创新的 GD32VF103 等。

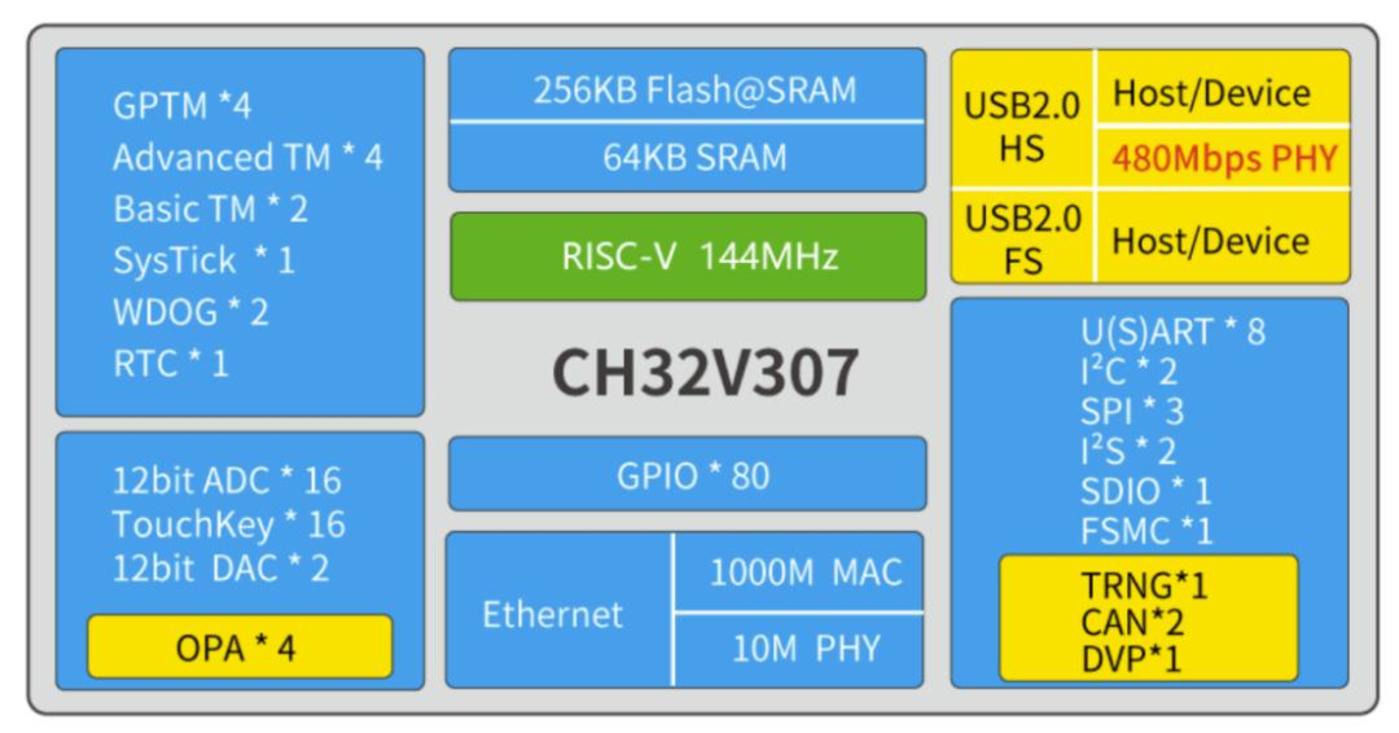

- 沁恒微 CH32V307

CH32V305/7 系列是基于 32 位 RISC-V 设计的互联型微控制器,配备了硬件堆栈区、快速中断入口,在标准 RISC-V 基础上大大提高了中断响应速度。加入单精度浮点指令集,扩充堆栈区,具有更高的运算性能。扩展串口 UART 数量到 8 组,电机定时器到 4 组。提供 USB2.0 高速接口 (480Mbps) 并内置了 PHY 收发器,以太网 MAC 升级到千兆并集成了 10M-PHY 模块。

CH32V307 具有高性能、低功耗、丰富的外围接口和高度可扩展性等优点。其具有可靠的产品和技术支持,使得 CH32V307 芯片在工业控制、汽车电子、消费电子等领域得到了广泛应用。

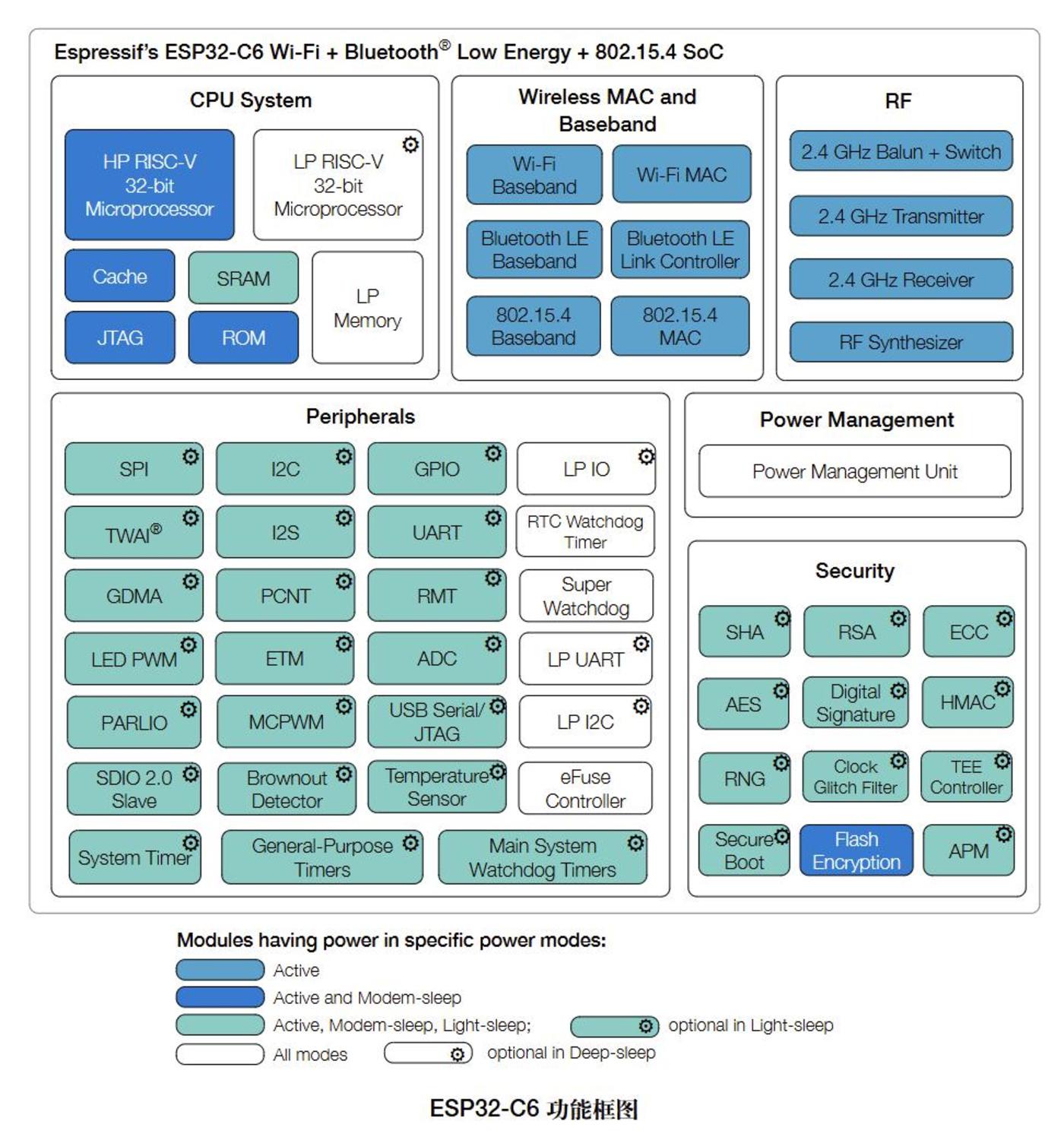

- 乐鑫科技 ESP32 系列

乐鑫科技深耕物联网无线通信 SoC 芯片领域,是全球 Wi-Fi MCU 细分领域龙头供应商,为 AIoT 终端厂商提供一站式解决方案。

2021 年 4 月,乐鑫科技宣布推出首款集成 Wi-Fi 6+Bluetooth 5(LE) 的 32 位 RISC-V SoC,标志着公司在产品硬件设计阶段不再依赖授权 MCU IP。基于开源架构自研内核在未来降低 IP 授权成本的同时,增加了设计者扩展芯片架构的灵活性,将促进形成更加完整的 IP、工具链和软件生态系统。目前乐鑫科技已经在 AI 硬件加速、AI 压缩算法等方面拥有了丰富的技术积累,已发布的 EPS32-C、H、P 系列全线产品均使用基于 RISC-V 的自研指令集。

乐鑫科技的 ESP32-C6 于 2025 年 2 月 20 日获得 PSA Certified Level 2 认证。这一重要突破使 ESP32-C6 成为全球首款基于 RISC-V 架构获此认证的芯片。

ESP32-C6 是乐鑫首款支持 Wi-Fi 6 的 SoC,集成 2.4 GHz Wi-Fi 6、Bluetooth 5 (LE) 和 802.15.4 协议,能够为物联网产品提供行业领先的射频性能、完善的安全机制和丰富的内存资源。它搭载一个时钟频率最高 160 MHz 的高性能 RISC-V 32 位处理器,和一个时钟频率最高 20 MHz 的低功耗 RISC-V 32 位处理器,内置 512 KB SRAM,320 KB ROM,并支持外接 flash。ESP32-C6 拥有 30 个 (QFN40) 或 22 个 (QFN32) 可编程 GPIO 管脚,支持 SPI、UART、I2C、I2S、RMT、TWAI、PWM、电机控制 PWM 和 SDIO。它还集成了一个 12 位 ADC 和一个温度传感器。

低功耗芯片 ESP32-C6 系列专为物联网 (物联网) 设备而设计,应用领域包括智能家居、工业自动化、医疗保健、消费电子产品等。

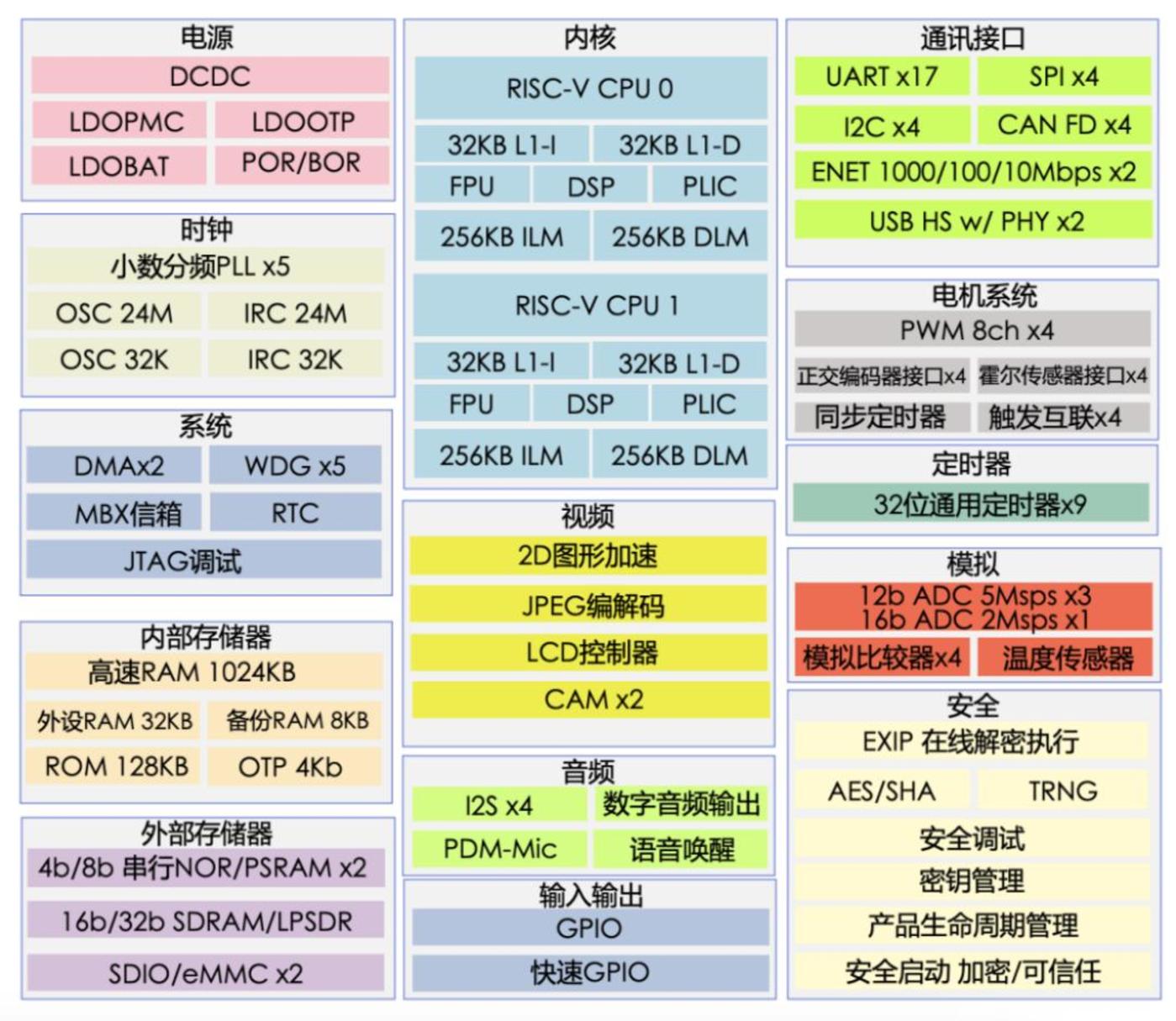

- 先楫 HPM6750 系列

先楫的 HPM6750 系列,采用双 RISC-V 内核,主频高达 800MHz , 凭借先楫半导体的创新总线架构、高效的 L1 缓存和本地存储器, HPM6750 在发布之际创下了 MCU 高于 9000 CoreMark 和 4500 以上的 DMIPS 性能新记录,为边缘计算的应用提供了极大的算力。

外设丰富,是先楫 HPM6750 的优点之一。

HPM6000 全系列产品支持双精度浮点运算及强大的 DSP 扩展,内置 2MB SRAM,并提供了丰富的多媒体功能,马达控制模块和通讯接口。HPM6000 系列的多媒体模块包括硬件图形加速,双摄像头,可支持高达 1366X768, 60FPS 的 LCD 显示, 以及多路语音和数字麦克风接口。马达控制模块包括多个高速和高精度的模数转换器 (ADC),多组纳秒级高分辨率 PWM 及模拟比较器等;通讯接口包括了两个千兆实时以太网,支持 IEEE1588,两个内置 PHY 的高速 USB,四路 CAN-FD 及丰富的 UART,SPI,I2C。

在安全方面,HPM6000 系列微控制器提供安全启动保证了启动代码不可篡改,防止软件恶意代码克隆及非法代码执行;集成 AES-128/256、SHA-1/256 加速引擎,支持密钥管理和保护;ROM 集成 Flash loader,支持代码加密烧写和升级。HPM6000 产品系列范围宽广,包括多核 HPM6750 及单核 HPM6450 选项,及入门级的 HPM6120 版本。

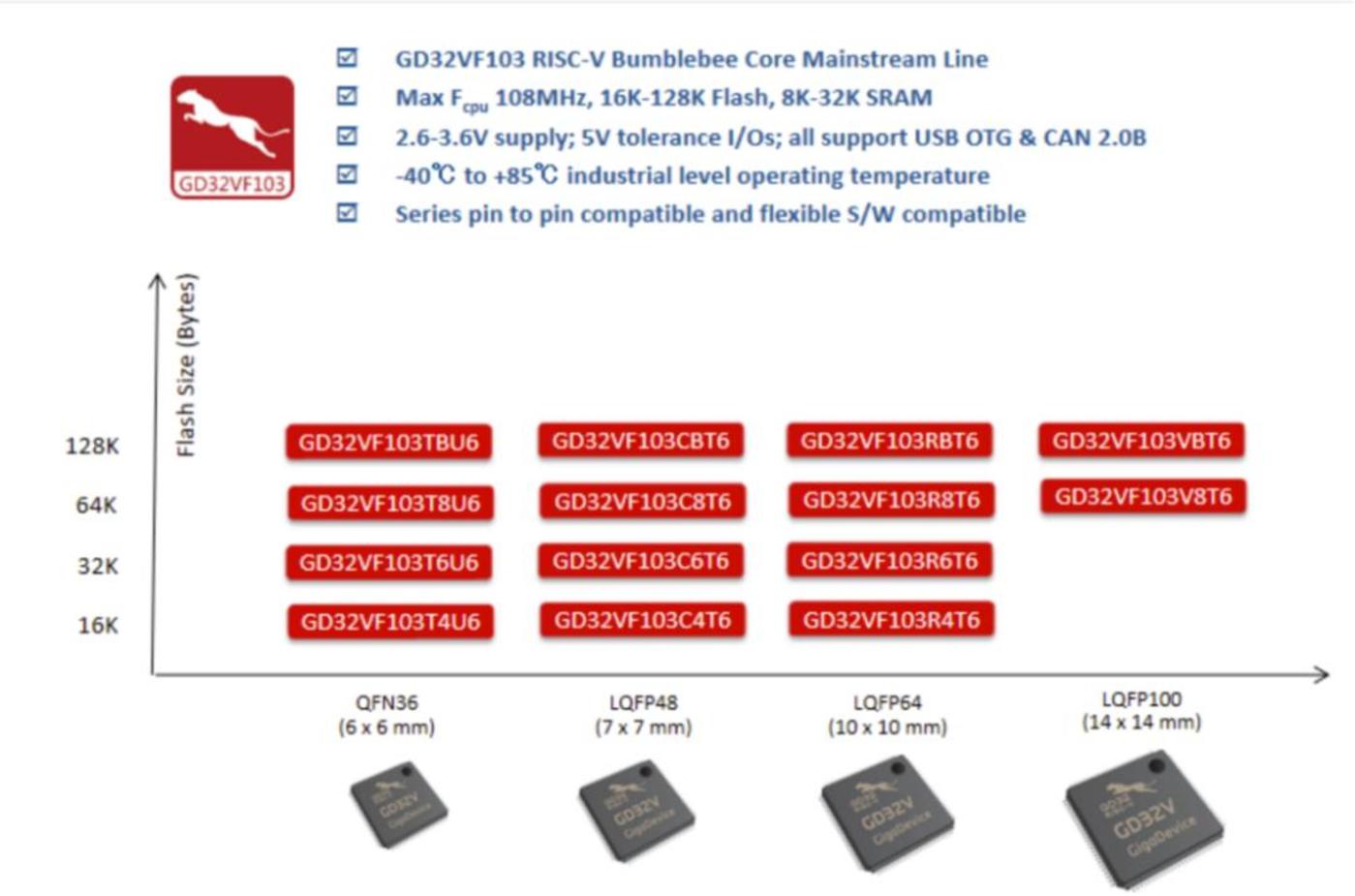

- 兆易创新 GD32VF103

GD32VF103 系列是全球首个基于 RISC-V 内核的 32 位通用 MCU 产品,其处理器内核拥有先进的微架构设计以权衡性能和面积的要求,特别适合物联网以及其他超低功耗场景应用。

GD32VF103 系列采用了全新的基于开源指令集架构 RISC-V 的 Bumblebee 处理器内核,是兆易创新携手 RISC-V 处理器内核 IP 和解决方案厂商芯来科技面向物联网及其它超低功耗场景应用自主联合开发的一款商用 RISC-V 处理器内核——Bumblebee。该内核设计了二级变长流水线微架构,配备精简的指令预取单元和动态分支预测器,并融入多种低功耗设计方法。能够以二级流水线的代价,达到传统架构三级流水线的性能和频率,实现了业界一流的能效比与成本优势。

GD32VF103 在最高主频下的工作性能可达 153 DMIPS,CoreMark 测试也取得了 360 分的优异表现,相比 GD32 Cortex-M3 内核产品性能提升 15% 的同时,动态功耗还降低了 50%,待机功耗更是降低了 25%。

因此,GD32VF103 系列能够满足主流型开发需求,以均衡的处理效能和系统资源为 RISC-V 进入市场主流应用提供了高性价比的创新之选。

RISC-V CPU 芯片

得益于 RISC-V 简化的架构,与传统 CPU 架构相比,它具有更高的性能和更低的功耗,这是支持 AI 革命的一个良好起点。

而最近,随着一系列热点事件的发布,基于 RISC-V 架构的服务器 CPU 迅速 「破圈」,闯入大众视野。

阿里巴巴达摩院旗下品牌玄铁,一直是 RISC-V 市场打头阵的种子选手。

回顾玄铁 RISC-V CPU IP 的发展历程:2018 年,玄铁首款 RISC-V 架构处理器 IP 玄铁 E902 发布;2019 年,发布了主频可高达 2.5GHz 的玄铁 C910 处理器,刷新了当时 RISC-V 处理器的性能纪录;2023 年 11 月,玄铁推出高性能 RISC-V 处理器 C910 的迭代产品 C920,主频提升到 3GHz。

AI PC 是玄铁处理器的主要应用场景之一。据悉,基于玄铁 C920 处理器的 AI PC 概念机已经跑通 Llama、Qwen、DeepSeek 等开源模型,打通从开源硬件架构到开源操作系统、再到开源 AI 模型的开源 AI 全链路。

玄铁 C920 采用 12 级多发乱序流水线,典型工作频率>2.5GHz,标配单精度浮点单元,并可进一步选配高性能乱序矢量运算单元。同时具备出色的访存能力,支持高性能数据预取技术。可以应用在有高并发算力要求的人工智能、自动驾驶等场景。

C920 核内子系统主要包含:指令提取单元 (IFU)、指令译码单元 (IDU)、整型执行单元 (IU)、浮点单元 (FPU)、矢量执行单元 (VU)、存储载入单元 (LSU)、指令退休单元 (RTU)、虚拟内存管理单元 (MMU) 和物理内存保护单元 (PMP)。

C920 多核子系统包含:数据一致性接口单元 (CIU)、二级高速缓存、主设备接口单元、可配置的 AXI4.0 设备一致性接口 (DCP,Device Coherence Port)、平台级中断控制器 (PLIC)、计时器和自定义多核单端口调试框架。

今年 2 月,玄铁宣布其基于开源 RISC-V 架构首款服务器级中央处理器 (CPU)IP 核——玄铁 C930,于今年 3 月开始交付。

- 香山 「昆明湖」

中国科学院计算技术研究院、北京开源芯片研究院、中国科学院大学联合推出了 「香山」 开源高性能 RISC-V 处理器项目,主要面向的就是高性能应用。

2021 年,「香山」 系列第一代开源高性能 RISC-V 处理器核 「雁栖湖」 正式发布,是同期全球性能最高的开源处理器核。2023 年 5 月,第二代 「香山」 系列开源高性能 RISC-V 处理器核 「南湖」 正式发布,当时也成为了国内首款对标 Arm Cortex-A76 的高性能开源 RISC-V 处理器核;此次推出的第三代 「香山」 系列开源高性能 RISC-V 处理器核则是 「昆明湖」,对标 Arm Neoverse N2 内核。

据介绍,第三代 「香山」 开源高性能 RISC-V 处理器核,设计工艺为 7nm,主频达到 3GHz,SPECINT2006 评分为 15 分/GHz,性能对标 Arm Neoverse N2 内核,可广泛应用于服务器芯片、AI 芯片、GPU、DPU 等高端芯片领域,可以作为先进计算产业提供开源共享的共性底座技术。

中科院大学教授、中科院计算所研究员包云岗表示,目前 CPU 领域还没有一个像 Linux 那样的开源主线,因此业界需要一个开源的高性能 RISC-V 核,既能被工业界广泛应用,又能支持学术界试验的创新想法。

RISC-V DSP

DSP 是一类嵌入式通用可编程微处理器,最大的优势是能够实时高速处理数字信号,且比 CPU、GPU、FPGA 功耗更低,广泛应用于通信、计算、消费电子和自动控制等领域。

目前 DSP 市场由美国 TI、ADI 等企业主导,国内企业占有率较低,尚处于起步阶段。

中科昊芯从 DSP 的内核到算法均为自主研发,全球首款基于 RISC-V 指令集的 DSP——Haawking-HX2000 系列,专为工业自动化、光伏储能及数字电源等高实时性场景设计,覆盖车规级 DSP、高性能 DSP、主流 DSP 和高性价比 DSP,可应用于工业控制及电机驱动、数字电源、光伏、储能、新能源汽车、消费电子、白色家电等领域。

目前 Haawking-HX2000 系列的十多款芯片已流片,多款型号量产供货,年均供货量近千万片。中科昊芯还推出了 Haawking IDE、Haawking-Downloader 编程工具及 HXLink 系列仿真器等,优化集成开发环境,均已大规模商用。

从成功研发到出货 100 亿颗芯片,RISC-V 用了约 10 年时间,走完了传统架构 30 年的发展历程。2023 年,RISC-V International 首席执行官 Calista Redmond 在 RISC-V 峰会中表示,未来几年 RISC-V 采用率将以 40% 年复合增长率增长,2030 年 RISC-V 架构芯片更有望突破 160 亿颗。据统计,RISC-V 基金已有高通、NVIDIA 和 Google 等超过 4000 名成员。